Alle Informationen zum Wettbewerb auf einen Blick.

Bundesministerin Anja Karliczek kürte die Preisträger im Rahmen einer virtuellen Preisverleihung© BMBF/Hans-Joachim Rickel

Bundesministerin Anja Karliczek kürte die Preisträger im Rahmen einer virtuellen Preisverleihung© BMBF/Hans-Joachim Rickel

Methoden der Künstlichen Intelligenz (KI) erschließen immer neue Anwendungen. Für die Verbreitung dieser rechenintensiven Technologie, besonders in mobilen Anwendungen, bildet hocheffiziente Mikroelektronik (KI-Hardware) die Basis. Um die Forschung in diesem Bereich voranzutreiben, mehr KI-Expertise in Deutschland aufzubauen und nicht zuletzt Ansätze zu erarbeiten, die das Potenzial für Sprunginnovationen bergen, führt das Bundesministerium für Bildung und Forschung (BMBF) den Pilotinnovationswettbewerb „Energieeffizientes KI-System“ durch.

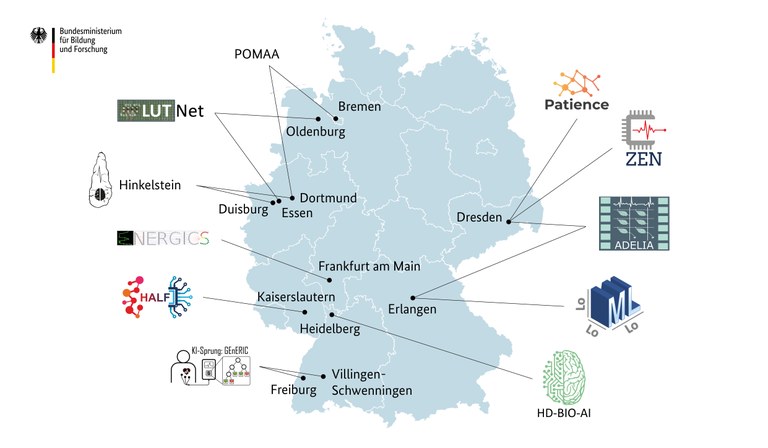

Der Wettbewerb startete am 1. Oktober 2019 im Vorfeld der Gründung der Agentur für Sprunginnovationen SprinD. Elf Forschungsteams wurden ausgewählt, um ihre Vorstellungen von einem energieeffizienten KI-System in einen Demonstrator bis zum 31. Dezember 2020 umzusetzen. Dabei wurden die elf Teams vom BMBF insgesamt mit ca. 4 Mio. Euro unterstützt. An der Entwicklung leistungsfähiger und zugleich energieeffizienter KI-Hardware besteht national und international großes Interesse, da die industrielle Umsetzung solch neuer Ansätze mit hohen technischen und wirtschaftlichen Risiken verbunden ist.

Übersicht aller Projekte des Wettbewerb

Im Pilotinnovationswettbewerb erarbeiteten elf Teams von Hochschulen und Forschungseinrichtungen in Konkurrenz die effizienteste Lösung für KI-Elektroniksysteme. Diese Systeme sollten am Beispiel von EKG-Daten möglichst energieeffizient KI-Berechnungen durchführen, die zuverlässig das Krankheitsbild Vorhofflimmern erkennen lassen. Hierfür standen reale Patienten-Daten (anonymisierte EKG) als Trainingsdaten zur Verfügung, um die KI-Systeme anzulernen. Am Ende der Wettbewerbsphase sollten alle Systeme anhand bisher unveröffentlichter EKG-Daten zeigen, dass sie die geforderte hohe Genauigkeit zum Erkennen von Vorhofflimmern erreichen. Sieger des Wettbewerbs sind die Teams mit den energieeffizientesten Systemen.

Die Aufgabe des Wettbewerbs war es, energieeffiziente Mikroelektronik zu entwickeln und damit das Krankheitsbild Vorhofflimmern am menschlichen Herzen mit Methoden der Künstlichen Intelligenz zu erkennen. Die genaue Art und Implementierung der KI wurde bewusst offengelassen, um innovative Ideen auf der Seite der Mikroelektronik zu fördern. Jedoch sollten die KI-Methodik und die entwickelte Elektronik zwingend auch auf andere potenzielle Anwendungsfälle übertragbar sein.

Die von der Charité – Universitätsmedizin Berlin zur Verfügung gestellten realen Patienten-EKG waren komplett anonymisiert und entsprachen den strengen Vorgaben der Datenschutz-Grundverordnung. Diese Daten wurden erstmals ausgewertet und sind bis dato in keiner anderen Weise veröffentlicht. Die EKG-Daten wurden von zertifizierten medizinischen Geräten erfasst. Alle EKG-Daten wurden von Kardiologen der Charité im Vorfeld hinsichtlich des Vorhofflimmerns begutachtet und entsprechend annotiert. Die Neuronalen Netze der KI-Systeme wurden mit einem Teil des gesamten Datensatzes angelernt. Die Messung und Evaluierung der Wettbewerbsbeiträge wurde mit einem anderen Teil des Datensatzes durchgeführt. Es standen insgesamt ca. 16.000 EKG zur Verfügung.

Um eine Vielzahl verschiedener technologischer Lösungsansätze zu ermöglichen und dennoch eine faire und objektive Bewertung sicherzustellen, wurde der Wettbewerb in drei technologische Kategorien gegliedert. Die Siegerteams wurden pro Kategorie bestimmt. Details zu den technologischen Kategorien FPGA, ASIC 130 Nanometer und ASIC 22FDX finden Sie weiter unten.

Jedes Siegerteam erhält als Preis die exklusive Möglichkeit, ein Forschungsprojekt zur weiteren Umsetzung seiner Idee mit Anwendungspartnerinnen und -partnern mit einem Budget von 1 Mio. Euro beim BMBF einzureichen. Gemeinsam in einem Verbund mit Industrie und - idealerweise - Anwendern sollen die Siegerteams ihre disruptiven Lösungsansätze und Ideen zu mikroelektronischen Systemen weiterentwickeln und in Anwendungen überführen.

In der Wettbewerbsrunde wurden die teilnehmenden Projekte und ihre Teams bereits vom BMBF (mit insgesamt ca. 4 Mio. Euro) finanziell unterstützt, da die Forschungs- und Laborarbeiten für konkrete Anwendungen (wie die Wettbewerbsaufgabe) zeitaufwändig und kostspielig sind.

Zur Teilnahme am Wettbewerb haben sich deutschlandweit 27 Teams aus Hochschulen und Forschungseinrichtungen beworben, von denen elf Teams für die Finalrunde ausgewählt wurden. Die Auswahl wurde von einem Fachbeirat begleitet, welcher auch eine fachliche Begutachtung der Messergebnisse am Ende der Finalrunde durchführte. Auf dieser Basis gab er eine Empfehlung für die Auswahl der Sieger an das Bundesministerium für Bildung und Forschung. Am 11. März 2021 wurden die Sieger im Rahmen einer Preisverleihung durch Bundesministerin Anja Karliczek verkündet.

Sieger in der Kategorie FPGA ist das Team um Dr. Jens Krüger vom Fraunhofer ITWM und das Team um Prof. Norbert Wehn von der TU Kaiserslautern mit dem Projekttitel: „Holistischer Ansatz zur Optimierung von FPGA Architekturen für tiefe neuronale Netze via AutoML – Automatisches Maschinenlernen (HALF)“.

Sieger in der Kategorie ASIC 130 Nanometer ist das Team um Prof. Dietmar Fey von der Friedrich-Alexander-Universität Erlangen-Nürnberg und das Team um Dr. Marco Breiling vom Fraunhofer IIS mit dem Projekttitel: „Low-Power Low-Memory Low-Cost EKG-Signalanalyse mit ML-Algorithmen (Lo3-ML)“.

In der Kategorie ASIC 22FDX gibt es zwei Sieger.

Zum Einen das Team um Prof. Christian Mayr von der TU Dresden mit dem Projekttitel: „Zeitreihenklassifikation mit Ereignisbasierten Neuronalen Netzen (ZEN)“.

Zum Anderen das Gemeinschaftsprojekt um das Team von Daniel Sanchez von der Hahn-Schickard-Gesellschaft für angewandte Forschung e. V. und das Team von Prof. Yiannos Manoli von der Albert-Ludwigs-Universität Freiburg mit dem Projekttitel: „Analyse von EKG Daten durch Energieeffiziente Entscheidungsbäume auf einem Rekonfigurierbaren ASIC (GEnERIC)“.

Beide Projekte konnten mit ihren ganz verschiedenen Lösungswegen hervorragende Energieeffizienzwerte erreichen und teilen sich den ersten Platz.

Der Wettbewerb wurde von einem Fachbeirat begleitet. Er bestand aus renommierten Experten aus der Mikroelektronik, den Anwendungsindustrien, der Künstlichen Intelligenz sowie der Medizin. Die Aufgabe des Beirats bestand in der fachlichen Beratung des Bundesministeriums für Bildung und Forschung (BMBF) bei der Auswahl und Evaluation der Wettbewerbsteams.

Teil des Beirats waren auch die beiden Partner vom Leibniz-Institut für innovative Mikroelektronik IHP und vom Chiphersteller Globalfoundries Dresden. Sie haben die Teilnehmenden des Wettbewerbs auf Basis ihrer Erfahrung in der Anwendung geeigneter Design-Tools bei der Umsetzung entsprechender Projekte beraten.

Zudem unterstützte das Deutsche Forschungszentrum für Künstliche Intelligenz DFKI die Entwicklung und Umsetzung der technischen Evaluierung der eingereichten Wettbewerbsbeiträge.

Prof. Wolfgang Ecker - Beiratsvorsitzender

Der Wettbewerb gliederte sich in drei technologische Kategorien. Damit wurden alle relevanten technologischen Umsetzungsmöglichkeiten adressiert. Jede Technologie hat ihre spezifischen Vorteile. Zudem sind alle Technologien in Deutschland verfügbar und können auch hierzulande produziert werden.

Ein FPGA, (englisch: Field Programmable Gate Array) ist im Prinzip eine Art integrierter Schaltkreis der Digitaltechnik, der alle typischen Bestandteile eines Prozessors beinhaltet. Die logische Verschaltung, die die Eigenschaften des Prozessors bestimmt, wird per Software geladen. Es ist somit ein programmierbarer Logik-Schaltkreis.

FPGA werden von verschiedenen Herstellern angeboten und sind nach der Programmierung sofort einsatzfähig.

Ein FPGA ist für die schnelle Entwicklung von Prototypen im Chipdesign vorgesehen. Er eignet sich besonders für geringe bis mittlere Stückzahlen von Mikroprozessoren, bei denen sich die Produktion von anwendungsspezifischen Schaltkreisen (ASICs) nicht lohnen würde, da diese zu zeitaufwendig und teuer wäre.

Der Lösungsansatz dieses Teams fokussiert einerseits auf den Energieverbrauch der Hardware und andererseits auf die Suche nach einer geeigneten neuronalen Netzwerktopologie. Da die Netzwerktopologie einen erheblichen Einfluss auf die Hardwarekomplexität hat und umgekehrt, wählte das Team einen holistischen Ansatz, der beide Aspekte und deren gegenseitigen Abhängigkeiten berücksichtigt. Dazu wurden neuste mathematische Methoden der automatisierten Topologiesuche verwendet. Die Suche greift dabei auf eine Bibliothek extrem energieeffizienter Hardware-Baublöcke zurück, die vom Team entwickelt wurden. Mit diesem automatisierten Ansatz ist nicht nur die Implementierung äußerst energieeffizienter FPGA, sondern auch eine Reduzierung der Entwicklungszeit von Monaten auf wenige Tage möglich. Ferner ist diese Methode auch für viele andere Anwendungsgebiete einsetzbar. In diesem Projekt verbindet sich die algorithmische Expertise für die automatisierte neuronale Netzsuche mit der Expertise für energieeffizienten Hardwareentwurf, die von den beiden Teams eingebracht wurden. Durch die Kombination dieser beiden Fachdomänen ist eine neue Methode entstanden, die synergetisch beide Kompetenzen in sich vereint.

Der vom Team entwickelte Chip basiert auf der Heidelberger BrainScaleS Architektur und realisiert das Prinzip des neuromorphen Rechnens. Dabei werden die wesentlichen Strukturmerkmale des biologischen Nervensystems, nämlich Netze aus Neuronen, mittels elektronischer Schaltkreise nachgebildet. In den allermeisten Fällen wird diese Emulation mit Hilfe digitaler Berechnungen umgesetzt. Bei BrainScaleS ist dies anders: Hier übernehmen analoge Schaltungen diese Aufgabe. Anstelle von Zahlen werden hierbei die Zustände der Nervenzellen durch kontinuierliche Größen repräsentiert. Dadurch wird deutlich weniger elektrische Energie benötigt. Das entwickelte System könnte jahrelang den Herzschlag eines Menschen auf Vorhofflimmern überwachen und dabei lediglich von einer kleinen Knopfzellenbatterie mit Energie versorgt werden, so gering ist sein Stromverbrauch. Dennoch führt es dabei Milliarden von Rechenoperationen pro Sekunde aus. Um die EKG-Messungen der kranken von den gesunden Patienten zu unterscheiden, wurde im Chip ein besonderes Neuronennetzwerk nachgebildet: Ein sogenanntes tiefes gefaltetes neuronales Netz. Diese Netze haben sich im letzten Jahrzehnt als äußerst leistungsfähig herausgestellt. Oft sind sie aber zu energiehungrig oder zu teuer für portable Anwendungen. Hier kann der entwickelte Mikrochip einen möglichen Ausweg aufzeigen: Er ist preiswert in der Herstellung, da er aufgrund seiner analogen Arbeitsweise mit kostengünstigen Produktionsmethoden gefertigt werden kann. Gleichzeitig bietet er aber dieselbe Rechenleistung bei minimalem Energieverbrauch wie die modernsten digitalen Technologien.

Der Wettbewerbsbeitrag von LUTNet stellt eine einfach anwendbare Methode bereit, um eine Vielzahl unterschiedlicher KI-Anwendungen in energieeffiziente Hardwareimplementierungen umzusetzen. Dabei setzt er nicht primär auf die Entwicklung hochspezialisierter, ressourcensparsamer neuronaler Chipstrukturen (sogenannte Neuro-Chips), sondern hilft erfahrenen Entwicklerinnen und Entwicklern von KI-Lösungen ihr spezielles Anwendungsproblem effizient in konventionellen Hardwaretechnologien umzusetzen. Die Transformation der KI in eine Hardware-Implementierung erfolgt durch einen weitgehend automatisierten Prozess, der sich auf eine Basisbibliothek energieeffizienter KI-Hardware-Komponenten, z. B. für Faltungen, Pooling, etc. stützt. Die Verwendung dieser Methode verlangt nur sehr wenig Hardwarewissen, ermöglicht es aber gleichzeitig, verschiedene Zielplattformen zu testen und die jeweils beste auszuwählen. Aktuell adressiert LUTNet nur Convolutional Neural Networks (CNNs) als Basistechnologie für die KI und implementiert diese für FPGA eines bestimmten Herstellers. Eine Portierung auf andere Zielplattformen ist jedoch leicht möglich, da dies in der Methode bereits konzeptionell angelegt ist.

Das Projekt setzte sich das Ziel, einen photonischen, also auf Licht basierenden, Hardwarebeschleuniger zu konstruieren und zu bauen. Dieser Beschleuniger führt die Operation zur Multiplikation und Summation (MAC), einen wesentlichen Bestandteil eines CNN, photonisch aus, wodurch die angrenzende Elektronik (z. B. ein FPGA) entlastet wird und zuletzt eine Reduktion des Energieverbrauchs des Gesamtsystems erreicht werden kann. In diesem Projekt wurde der Encoder der photonischen Schaltung unter Verwendung der EPIC-Technologie (Electronic Photonic Integrated Circuit) des Leibniz-Institut für innovative Mikroelektronik entworfen und gebaut und kann mit einem angeschlossenen FPGA kommunizieren.

Die zweite und dritte Technologiekategorie bestehen aus sogenannten ASICs.

Ein anwendungsspezifischer integrierter Schaltkreis (englisch Application-Specific Integrated Circuit, ASIC) ist eine elektronische Schaltung, die als „fest verdrahteter“ integrierter Schaltkreis realisiert wurde. Die Funktion eines ASICs ist nicht mehr veränderbar, ein ASIC kann aber viel spezifischer angepasst werden – was in der Regel in nochmals wesentlich verbesserter Effizienz mündet. Die Herstellungskosten pro ASIC sind bei mittleren bis hohen Stückzahlen geringer als bei FPGA. ASICs werden weltweit von Auftragsherstellern nach Kundenanforderung gefertigt und normalerweise nur an diese geliefert. Üblicherweise dauert die Entwicklung und Fertigung eines ASIC bis zum fertigen Prozessor circa 12 Monate. Die Entwicklungskosten sind hoch und lohnen sich bei geringen Stückzahlen in der Regel nicht.

Beide folgende Halbleitertechnologien zur Herstellung von ASICs werden in Deutschland gefertigt.

Die Designs in dieser ASIC Kategorie werden für die 22nm Fully-Depleted SOI Technologie (22FDX) realisiert und können bei GLOBALFOUNDRIES in Dresden gefertigt werden. Durch die besondere Eigenschaft der Ansteuerung mittels des sogenannten Back-Gate ist die 22FDX Technologie hervorragend geeignet, um energiesparsame Schaltkreise für das Internet der Dinge (IoT), Kommunikationsanwendungen und "Edge-Computing" zu realisieren.

Dieses Team fokussierte sich auf den Entwurf eines analogen Inferenz-Beschleuniger ASICs in 22 FDX® GLOBALFOUNDRIES-Technologie. Um den neuronalen Netzwerkalgorithmus als ASIC zu realisieren, wurde eine Prozedur für Hardware und Software Co-Design entwickelt. Mit den entwickelten Bausteinen ist eine automatische Generierung von Schaltplänen und Layouts der vorliegenden neuronalen Netzwerkalgorithmen möglich. Das ASIC-Design selbst beinhaltet zwei Hauptblöcke: Das neuronale Netzwerk und ein Mixed-Signal-Frontend. Diese Lösung zeichnet sich durch außerordentliche Flexibilität aus: Sie kann mit kleinen Änderungen für eine Vielzahl anderer Klassifizierungsprobleme von Zeitreihensignalen, wie z. B. Audiosignalen oder Vibrationssignalen angewendet werden. Des Weiteren ist es möglich, die Gewichtswerte des Netzwerkes jederzeit zu aktualisieren. Der ADELIA-ASIC erreicht in der Simulation einen Energieverbrauch von nur 449,95 nJ per Inferenzdurchgang, bestehend aus 235,42 nJ für den Mixed-Signal Frontend und 214,53 nJ für das neuronale Netzwerk. Somit ergibt sich ein mittlerer Leistungsverbrauch von 1,2 mW.

Das Team verfolgte eine ASIC Implementierung in einem 22 Nanometer Prozess des Technologiepartners Globalfoundries. Im Gegensatz zum allgemeinen Deep Learning Trend kommt dabei ein Ansatz des klassischen maschinellen Lernens zum Einsatz: der Entscheidungsbaum, bzw. das Entscheidungsbaumensemble. Dieser ist zwar weniger mächtig als beispielsweise ein neuronales Netz, kann dafür allerdings weniger komplexe Aufgabenstellungen mit erheblich geringerem Ressourcenaufwand lösen. Die wesentlichen Erfolgsmerkmale dieses Beitrags sind zum einen die enge Verzahnung der Entwicklung von Softwarealgorithmus und Hardwareimplementierung. Dabei wurden über den gesamten Entwicklungszeitraum kontinuierlich Eigenschaften und Kosten der Hardware in die Optimierung des Algorithmus auf Softwareebene zurückgeführt. Zum anderen ist die innovative Implementierung der Baumstruktur in Hardware zu nennen. Sowohl die Einteilung der Merkmale in die im Modell enthaltenen Schwellwertintervalle als auch die komprimierte Abbildung der Baumstruktur auf Speicherinhalte tragen weiter zur Reduktion der zu verarbeitenden Datenmenge und des Energieverbrauchs bei. Im Wettbewerb sollen EKG-Datensätze über zwei Minuten verarbeitet werden. Es ist zu erwarten, dass durch diese Lösung eine Energie von weniger als 42nJ erforderlich sein wird – in etwa 1/10000 der Energie eines Flügelschlages eines Schmetterlings.

Neuronale Netze können ganz unterschiedlich aufgebaut sein. Kann man also Neuronale Netze bauen, die sowohl genau in ihren Vorhersagen als auch möglichst energieeffizient gleichzeitig sind? Wenn man eine solche Architektur gefunden hat, kann man diese auch auf einem speziellen Mikrochip unterbringen, um noch energieeffizienter zu sein? Ein Problem bei der Suche ist: Es ist nahezu unmöglich, viele verschiedene Architekturen auf gut Glück durchzuprobieren und zu testen, um die beste oder energieeffizienteste Architektur zu finden, dafür dauert der Lernprozess und die Transformation in einen Mikrochip viel zu lang. Kann man also wiederum künstliche Intelligenz und maschinelles Lernen einsetzen, um bei der Suche zu helfen? Hierum ging es in POMAA: Optimiere die Architektur von neuronalen Netzen für den Einsatz auf einem Mikrochip. POMAA hat gezeigt, dass dies tatsächlich möglich ist. Hierdurch können neuronale Netze schlanker, schneller und effizienter gemacht werden – und der Entwurf eines passenden Mikrochips gleich mit erstellt werden. Dies ermöglicht den Einsatz von neuronalen Netzen in vielen verschiedenen Anwendungsgebieten, bei denen ein niedriger Energieverbrauch zählt, etwas in der Robotik oder der Medizintechnik.

Die im Projekt ZEN entwickelte Hardware-Lösung auf Basis rekurrenter neuronaler Netze ist flexibel einsetzbar und gleichzeitig ähnlich energieeffizient wie die Ansätze mit händisch optimierten Merkmalen. Der Ansatz stützt sich auf eine ereignisbasierte Verarbeitung, die an die Arbeitsweise der Neuronen im menschlichen Gehirn angelehnt ist und den Rechenaufwand stark reduziert. Hierbei werden Rechenschritte nur bei Änderungen in den Eingangssignalen oder Zwischenwerten ausgeführt. Für die Wettbewerbsaufgabe waren damit im Mittel lediglich 12 Rechnungen pro Zeitschritt nötig. Zum Ermitteln von Signalmerkmalen wird eine Filterbank mit anpassbarer Struktur verwendet. Die Parameter der Filter werden zusammen mit dem rekurrenten neuronalen Netz durch maschinelles Lernen für eine Klassifikationsaufgabe benutzt. Dadurch sind Anpassungen an neue Anwendungen mit geringem Entwicklungsaufwand möglich. Die Verarbeitung wird bei ausreichender Sicherheit des Ergebnisses sofort abgeschlossen. Im Mittel war das nach nur 13 Sekunden einer EKG-Aufzeichnung der Fall. Die ZEN-Architektur kann die Wettbewerbsaufgabe mit lediglich 326 Byte Parameterspeicher erfolgreich lösen. Die ZEN-Hardware ist flexibel und skalierbar. Die Architektur der Filterbank und des neuronalen Netzes lässt sich beliebig konfigurieren. Durch eine systematische Implementierungsstrategie konnten die Realisierung und der Betrieb bei maximaler Energieeffizienz nachgewiesen werden. Durch den skalierbaren Ansatz ist nur eine Speichererweiterung erforderlich, um die Implementierung auch für deutlich komplexere Klassifikationsprobleme einsetzen zu können.

Die spezielle 130 Nanometer (130-nm-SiGeBiCMOS) Technologie des Leibniz-Instituts für innovative Mikroelektronik IHP in Frankfur an der Oder ist für Hochfrequenz- und Kommunikationsanwendungen hervorragend geeignet. Diese Technologie ist bekannt für einen der schnellsten Siliziumtransistoren der Welt und wird u.a. in Bereichen wie Radar für automatisierte Fahrten, Raumfahrt und dem Mobilfunk der 5. Generation eingesetzt (5G).

Das Projektteam behandelte die Fragen, ob ein komplexes Klassifikationsverfahren wie ein Deep Neural Network (DNN) auf einem analogen Chip implementiert werden kann und wie energieeffizient ein solcher Chip schwierige Probleme lösen würde. Als Lösung wurde ein Ansatz für das Lernen und Entwerfen von energieoptimierten, analogen Schaltkreisen für DNNs entwickelt. Ausgehend von einem Trainingsdatensatz wird hier ein DNN gelernt. Dieses wird mit Hilfe einer entworfenen Bibliothek von analogen Blockelementen automatisiert an die Hardwarebedingungen angepasst und als analoger Schaltplan generiert, was den Entwicklungszyklus für neue Anwendungen entscheidend verkürzen kann. Im Ergebnis wurde ein energieeffizienter, programmierbarer Analogchip entwickelt. Ein analoger Chip rechnet nicht wie digitale Chips mit Nullen und Einsen in ihren Schaltkreisen, sondern kann Abstufungen und zwischen diesen Werten nutzen. ENERGICS kombiniert eine Vielzahl von Ideen, die den Energieverbrauch, die Genauigkeit und die analoge Chipgröße optimiert haben. Dieser neue Ansatz wird es ermöglichen, komplizierte DNNs für eine Vielzahl von Anwendungen umzusetzen und eine Brücke zwischen modernen Erkenntnissen des maschinellen Lernens und energieeffizienter analoger Hardware zu schlagen.

In diesem Projekt wurde eine hocheffizienten KI-Methode und ihre technische Umsetzung als spezialisierte und deswegen äußerst energieeffiziente Digitalschaltung kombiniert. Als KI-Methode kam eine Variante neuronaler Netzwerke zum Einsatz, nämlich ein sogenanntes neuronales Faltungsnetzwerk. Dieses ist in der Lage sowohl charakteristische Eigenschaften der zu untersuchenden EKG-Signale automatisch aus Beispieldaten zu lernen, als auch die Entscheidung darüber zu treffen, ob Vorhofflimmern vorliegt oder nicht. Das gelernte Modell erreichte eine hohe Zuverlässigkeit und konnte besonders kompakt realisiert werden, so dass nur eine äußerst geringe Anzahl an Rechenoperationen zu dessen Auswertung erforderlich ist. Trotz aller Spezialisierung konnten die Rechenwerke im Aufbau flexibel gehalten werden, so dass sie durch neue Re-Konfiguration und Re-Parametrisierung als Bausatz für die Realisierung anderer Anwendungen dienen können.

Das Thema des Projekts ist die besonders energieeffiziente Verarbeitung von Zeitreihensignalen. Dafür wurde ein Chip für KI-Berechnungen (Deep Learning) entwickelt, in dessen Schaltung mehrere innovative Konzepte eingesetzt wurden. Durch die Verwendung von speziellen systolischen Arrays kann die zur Ablaufsteuerung benötigte Energie stark gedrückt werden. Es werden nur die drei Gewichtswerte -1, 0 und +1 verwendet sowie Normierungen mit Zweierpotenzen. Der Chip enthält nicht-flüchtige Speicher, sogenannte RRAMs, samt Ultra-Low-Power-Schaltungen zum Schreiben und Lesen, die genau diese ternären Gewichtswerte sehr effizient speichern können. Diese Speicher erlauben es, die Signalverarbeitung über lange Phasen schlafenzulegen, um keine Energie zu verbrauchen. Bei typischen Signalbandbreiten im (Sub-) kHz-Bereich fließen nämlich die Daten viel langsamer in den Chip ein, als sie verarbeitet werden können. Das Aufsammeln dieser Daten während der KI-Algorithmus schläft, gefolgt vom schnellen Aufwecken des Algorithmus dank des PRAMs, sowie einer kurzen KI-Verarbeitung kann deshalb bis zu 95% Energieeinsparung im Vergleich zu einem „Always-On“-System führen. Zusätzlich wurde viel Wert auf einen (noch) teil-automatisierten Entwurfsprozess gelegt. Dazu gehören auch neu entwickelte Tools für hardware-aware angepasstes Training eines neuronalen Netzes, z. B. für die verwendete extreme Quantisierung. Dieser Prozess kann auch für andere Probleme und Anwendungen eingesetzt werden. Das Projekt zeigt eindrücklich, welche Optimierungspotenziale durch eine enge Zusammenarbeit zwischen den Entwicklern von Algorithmen und digitalen sowie analogen Chip-Entwicklern gehoben werden können.